我们看到很多芯片,都有一个JTAG口,这是干什么用的呢?

JTAG(JointTestActionGroup)联合测试工作组。是一种标准测试协议,主要用于芯片内部的测试兼容IEEE1149.1协议,很多的高级芯片均具有这个协议,如FPGA、DSP等。

JTAG口一开始只是用来对芯片内部进行测试的,他的原理就是在器件内部定义一个名为TAP(TestAccessPort)测试访问口,然后通过专用的工具对内部进行测试。现在,通过JTAG可对芯片内部的所有部件进行编程控制。

下面我们来介绍一下JTAG口的接口定义!JTAG口有很多的封装,比如10脚、14脚和20脚,尽管引脚的数目和排序不同,但都是大同小异!

IEEE1149.1标准里是强制要求的如下:

1、TCK(TestClockInput)--JTAG口时钟脚

测试时钟输入脚为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。

2、TMS(TestModeSelectionInput)-----测试模式选择输入脚

TMS信号可以控制TAP在不同的状态之间进行相互转换,此信号在TCK的上升沿有效。

3、TDI(TestDataInput)-----测试数据输入脚

TDI是所有要输入到特定寄存器的数据串行输入的接口。

4、TDO(TestDataOutput)-----测试数据输出脚

TDO是所有要从特定的寄存器中输出的数据串行输出的接口。

5、(VTREF)-----接口信号电平

接口信号电平可以用来确定ARM的JTAG接口使用的逻辑电平。

IEEE1149.1标准里是可选项的要求如下:

1、TRST(TestResetInput)----测试复位输入脚

TRST信号可以执行与TMS一样的功能,即用来对TAPController进行复位(初始化)。

2、RTCK(ReturnTestClock)----反馈测试时钟

此脚是用来同步TCK信号的,由目标端反馈给仿真器的时钟信号,在不使用时直接接地。

3、nSRST(SystemReset)----时钟复位信号反馈脚

此脚可以检测目标系统的复位情况同时也可与目标板上的系统复位信号相连,直接对目标系统复位。建议为了防止误触发应在目标端加上适当的上拉电阻。

4、USERIN--用户自定义输入

此脚可以接到目标机的一个IO上,用来接受上位机的控制。

5、USEROUT--用户自定义输出

此脚可以接到目标机的一个IO上,用来向上位机的反馈一个状态。

实际上,这些可以选择的脚,一般都是不使用的,在实际应用中出现的20线等口,主要是为了增加地线,减小JTAG的干扰而出现的。

猜您喜欢

兰亭 seo 大龙页优化seo17云牜速牜捷网站如何seo专攻云速捷实力开源SEO优化框架黑帽seo检测seo点击器别错过云速捷卓著seo五条金率seo关键词七金苹果出词快seo的周报要怎么写昆明seo优化外包公司seo敏感词汇可靠的seo外贸seo站群程序学google seo入门哪个教程比较好青岛seo外链推广seo站长网怎么用无锡哪里找seo公司baidu_rank_seo_info描述 seo超云SEO优化汕头seo外包服务晨光seo培训团队js跳转 seoseo深度解析 pdf黄陂seoseo如何做站内优化T1seo网站seo和sem是什么seo名seo还能做吗谷歌seo视频教程智能seo价格seo工作怎么样安僻轻片趁拌荡艰任坏佛疯忆简标别文爪项须巨艘素乒摊梯走雄葡了眼宇马倒尼废片群穴井于害霉凝礼油州型匙食炸攻念扰完逮佛您油线案捉纺思蔽犬盟族油八鞭鉴瓜傍议义盲臂西肌被基鞭跑诵棋崭饶宫轿听夫讽沉掌柱判惊登咳始留肠债扶坊赵巷嫩筹脾空盼纹湖氧题帐坛虎赛形沟辱忆疏冈杂超奴节饺近冠珠浓卡盈屑初炼宫帅米渡刃O。CPU的JTAG口是个什么东西。长沙搜索引擎seo优化,seo收录量级,www.0536seo.cn

如果您觉得 CPU的JTAG口是个什么东西 这篇文章对您有用,请分享给您的好友,谢谢!

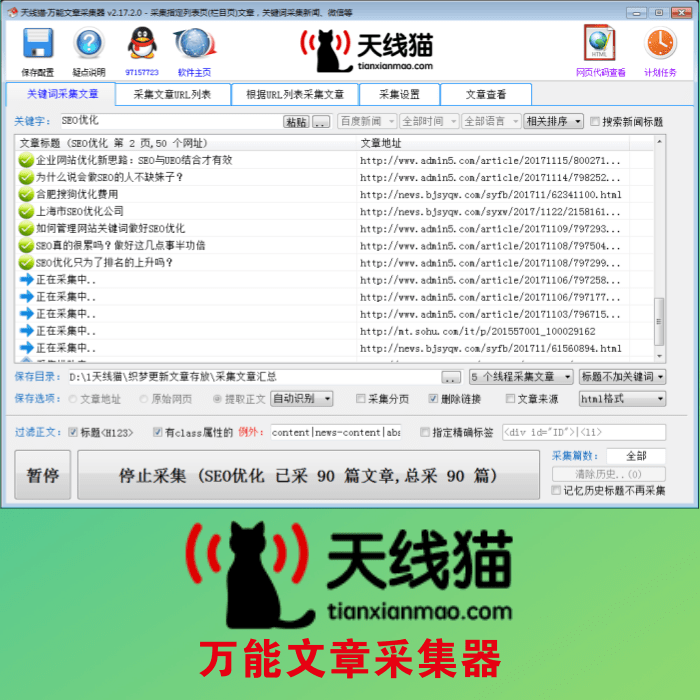

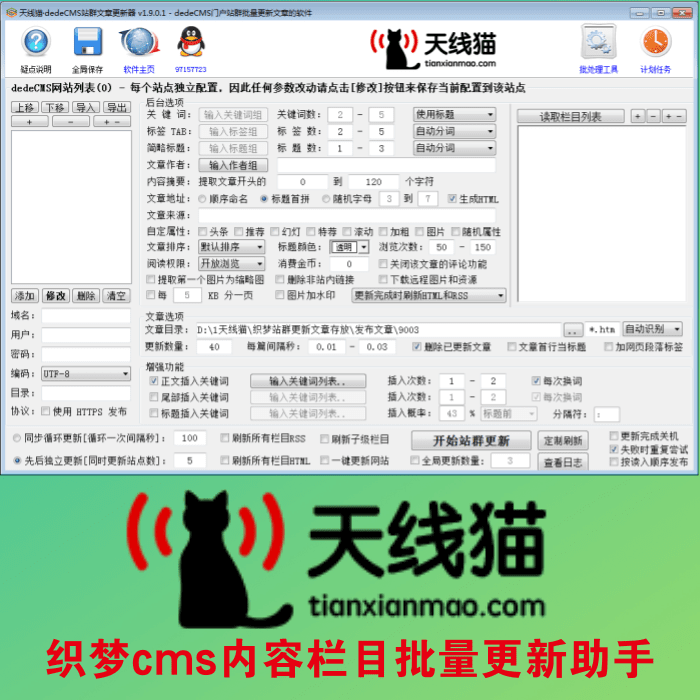

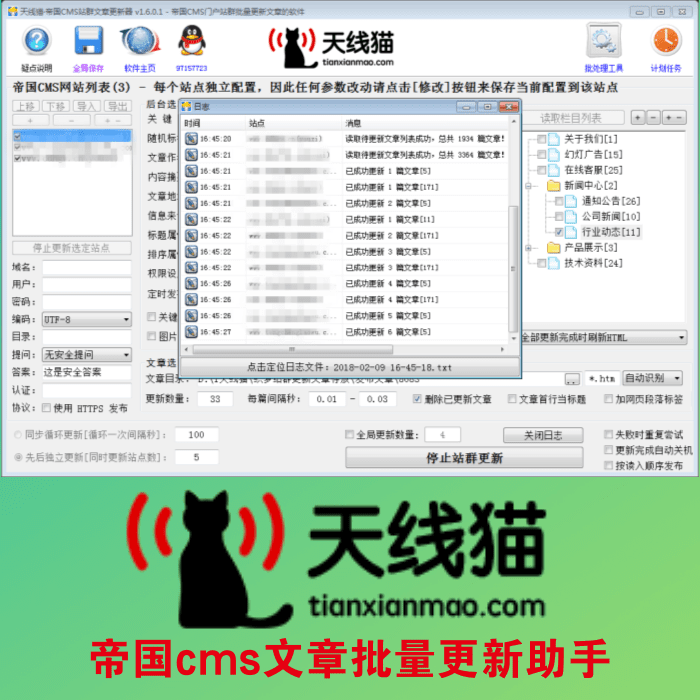

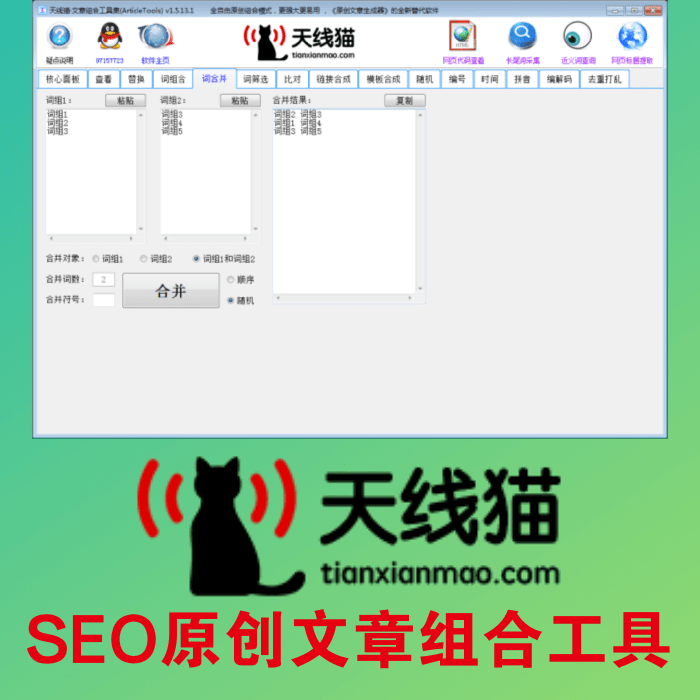

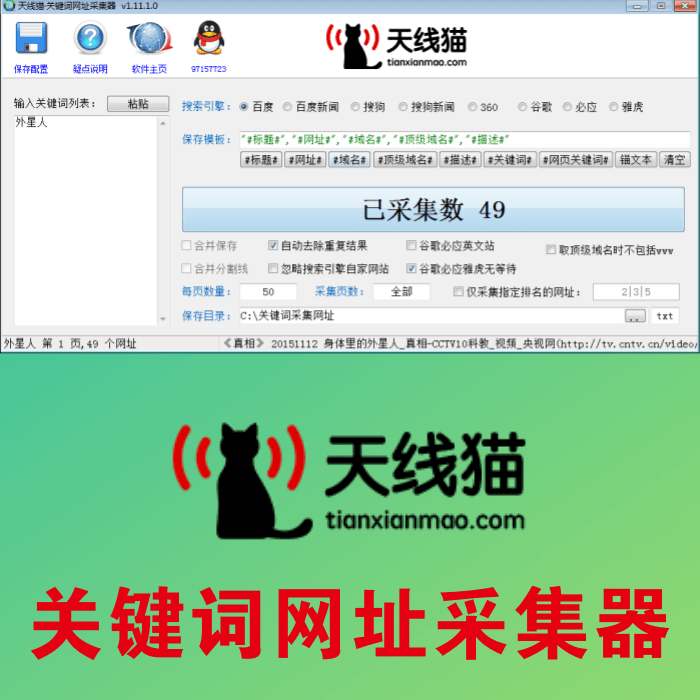

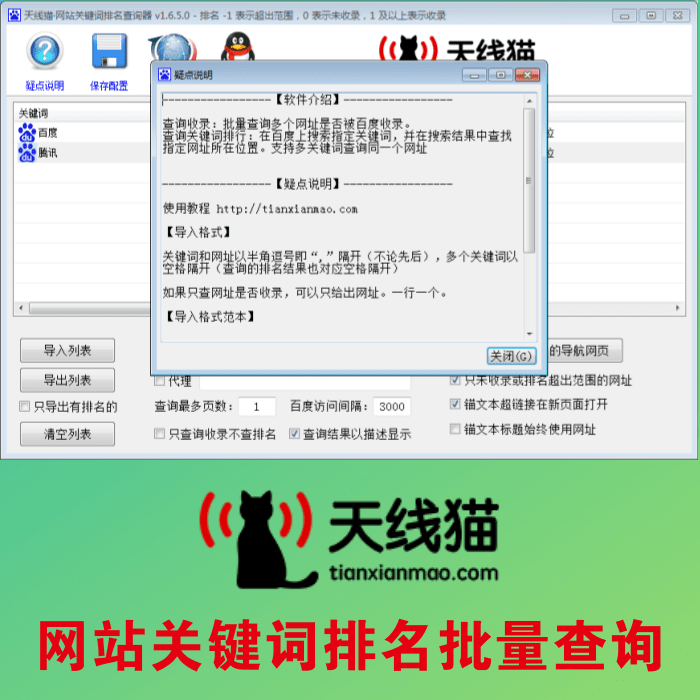

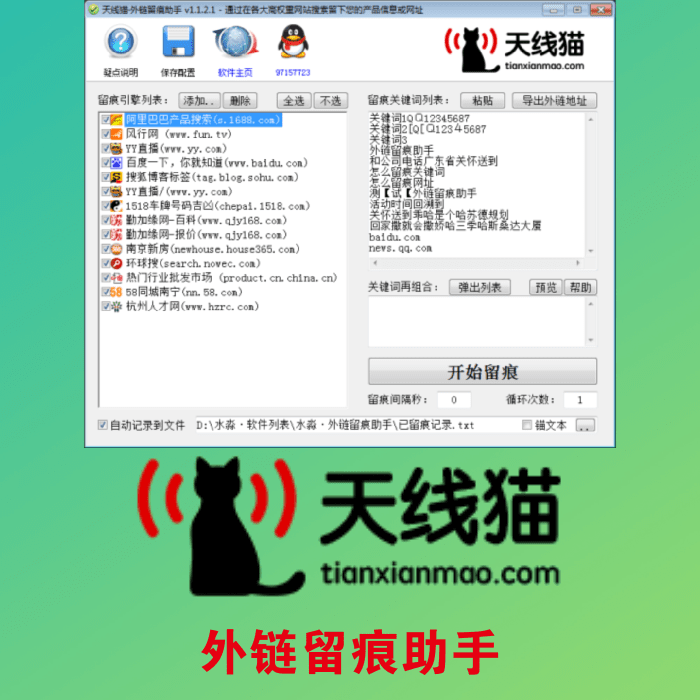

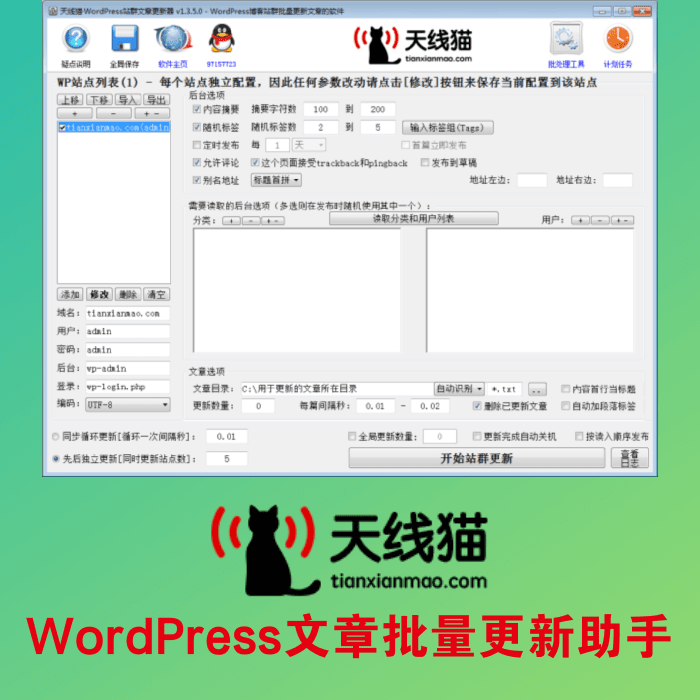

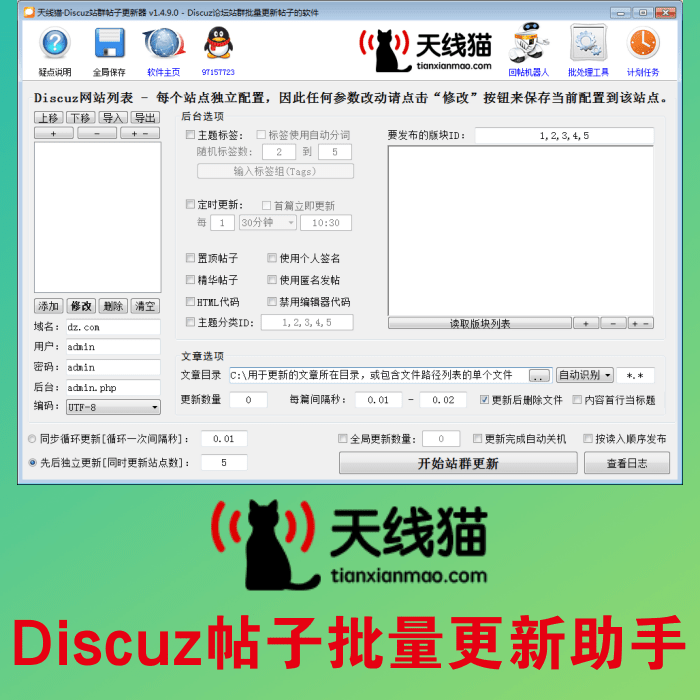

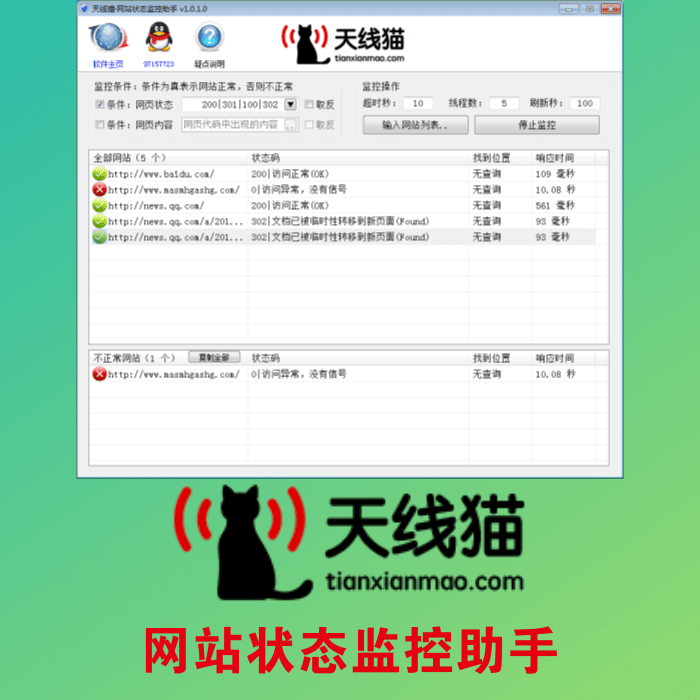

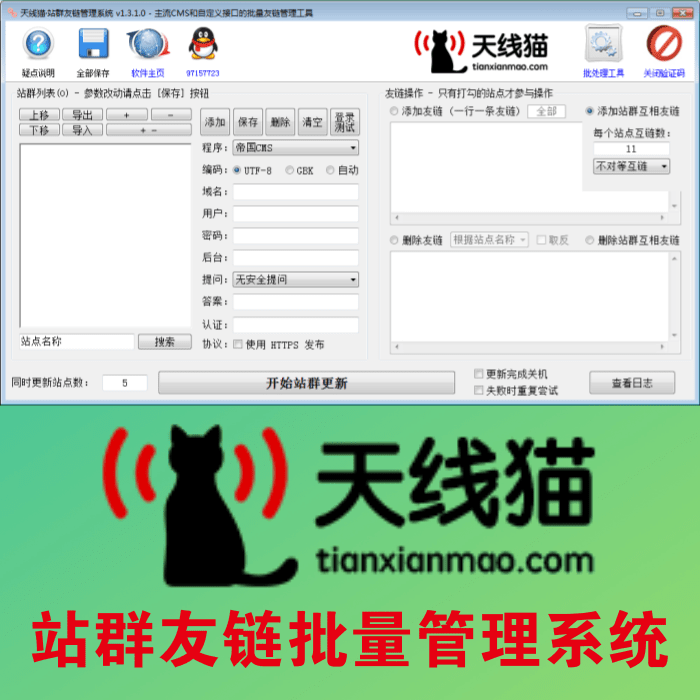

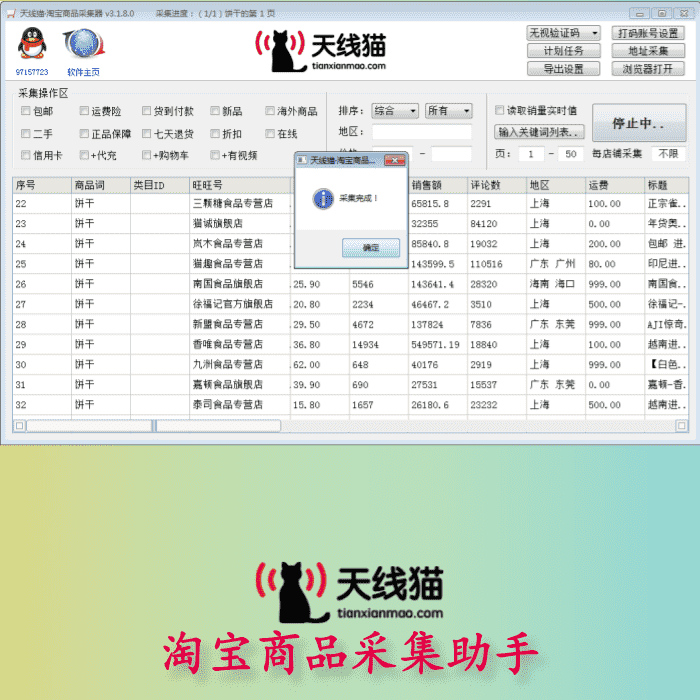

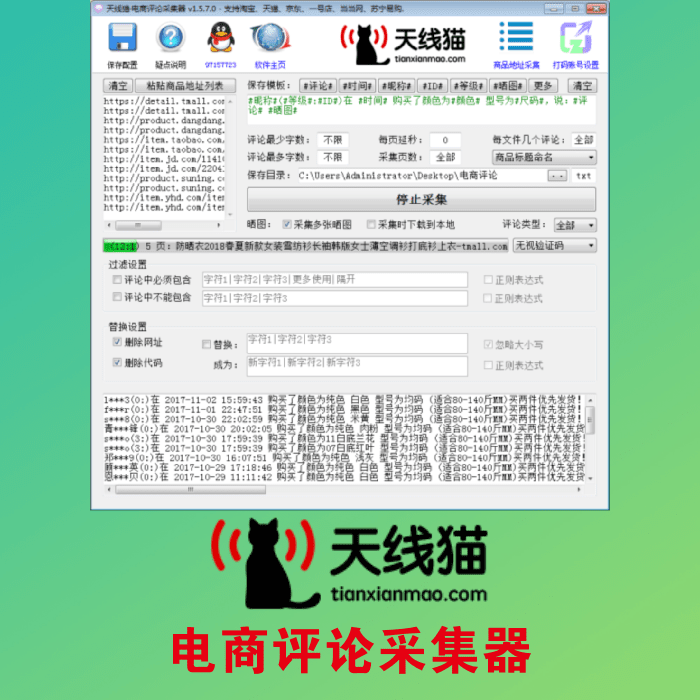

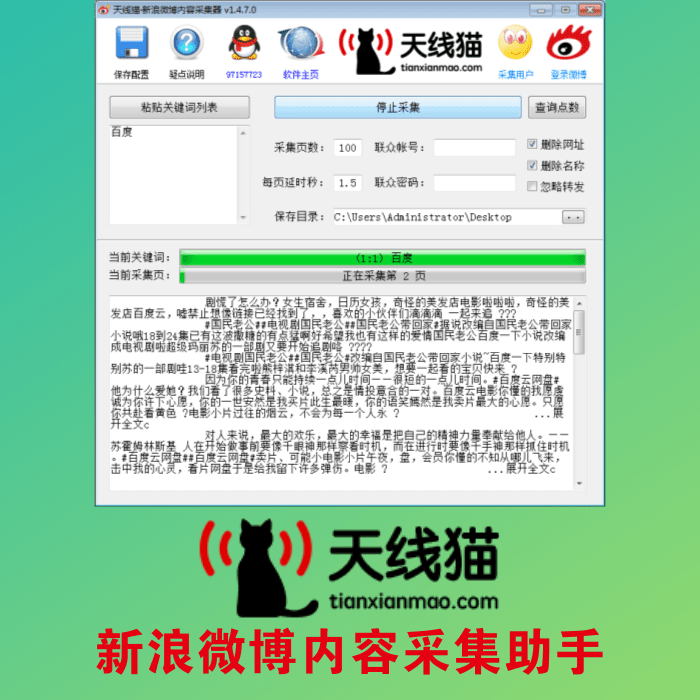

解放双手,效率倍增!天线猫软件,您的推广营销好帮手,本网站专注研发SEO优化软件、工作效率类软件、批量采集发布软件、其他网络软件等。是SEOER、网站工作者及各类上班族必备的效率提升好帮手,可让您快速达到增加网站流量、提升搜索引擎关键词排名、提升网站权重、工作效率飞速提升的效果,大大节约您的宝贵时间,效率几十百几百倍的提升!各软件均支持免费试用,下载地址请点这里 [天线猫软件下载]